Chip-Package-Board System Simulation

Model signal and power integrity from chip to package to board in one EM environment.

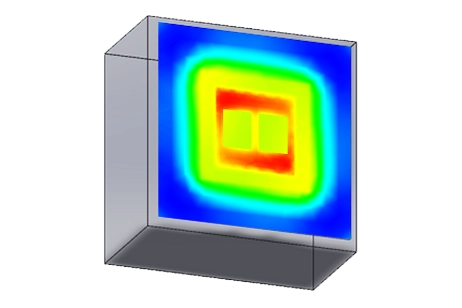

This application note models an Intel dual-die CPU as a dual-fed microstrip patch to study electromagnetic compatibility at 2.05 and 4.9 GHz. It compares S-parameters, field distributions, and temperature with and without a heatsink, and evaluates the effect of heatsink height. The results show that resonant frequencies and scattering parameters are dominated by the internal package, while the heatsink mainly influences thermal distribution, with simulations closely matching published measurement data.

This example model a single copper TSV in silicon with SiO₂ insulation and wave ports at top and bottom. S-parameter analysis (S11, S21) and field plots help you quantify insertion/return loss and mode behavior for TSV-based 2.5D and 3D IC interposers.