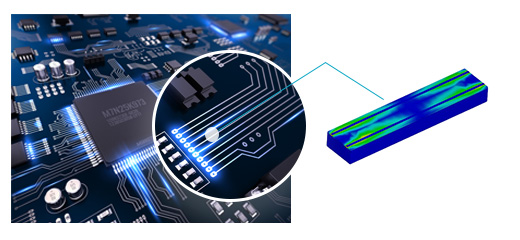

Over the last decade, the frequency of local clocks on chips and the speed of I/O drivers have continued to increase. Interconnects have become more complex with more functionality as integration technology continues to advance. Such advances enabled engineers to design circuits with remarkable enhancement in terms of higher I/O densities, more complex interconnects and reduced size through the use of TSV in 3D ICs. The designer, however, needs to consider the effects of high-speed signals in an IC design since continuously increasing clock frequencies and decreasing rise times may lead to important signal integrity issues. Signal integrity for high-speed PCB designs is critical for ensuring data can be passed between PCB components and to ensure signals can be correctly interpreted by a receiver. Signal integrity is affected by several factors: high frequency data speed, high density of interconnects and losses. A signal degradation can cause system problems such as bit errors, lost data packets, and others.

In this webinar, we will demonstrate how to build and simulate interconnects in a Flip-Chip Package. We will show how accurate 3D field simulation in conjunction with circuit simulation accurately capture the effects of data rate, vias and material losses on system performance, including the impact on Inter-Symbol Interference (ISI).